- #INTEL WATCHDOG TIMER DRIVER LOCATION IN DEVICE MANAGER HOW TO#

- #INTEL WATCHDOG TIMER DRIVER LOCATION IN DEVICE MANAGER SOFTWARE#

- #INTEL WATCHDOG TIMER DRIVER LOCATION IN DEVICE MANAGER CODE#

#INTEL WATCHDOG TIMER DRIVER LOCATION IN DEVICE MANAGER CODE#

I find this variant to be one of the more frustrating ones because, unless you are very careful about how many cycles your cleanup code takes to execute, the hardware may reset the system in the middle of cleanup! The MCU will give you a few extra clock cycles to do cleanup and then reset the MCU.

#INTEL WATCHDOG TIMER DRIVER LOCATION IN DEVICE MANAGER SOFTWARE#

In the interrupt handler, the software can decide to “feed” the watchdog to prevent the system from resetting.

#INTEL WATCHDOG TIMER DRIVER LOCATION IN DEVICE MANAGER HOW TO#

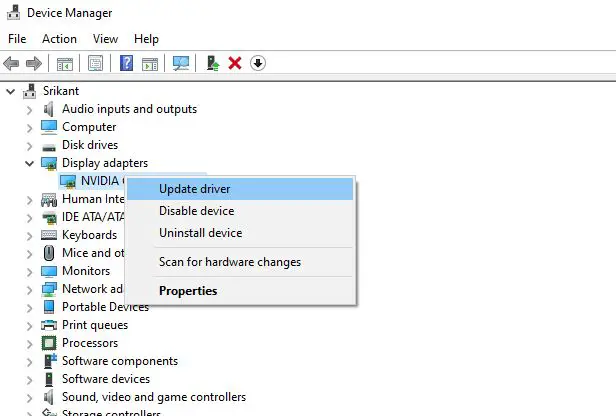

We will explore an example of how to do this with GDB later in the article.įun Fact: For Cortex-M’s, I’ve always been very impressed with the configuration options that STMicroelectronics exposes for STM32s via the DBGMCU component. In these scenarios, the debugger can be configured to issue register writes that pause or feed the peripheral. Not all hardware supports this feature however. That way, if you add a breakpoint and are inspecting code, you don’t have to worry about a watchdog firing. This almost always leads to issues going unnoticed until a release build is cut that could have been identified and fixed in the development phase instead.Ī less known fact is that most MCU vendors have special configurations that can be used while the system is halted to pause the watchdog timer. However, I would argue this is a big mistake. The watchdog is often disabled by developers for debug builds in an effort to prevent resets on boards actively being developed. How does the watchdog behave with a debugger? a “Power on Reset” (POR)) will disable the watchdog). Once enabled, only certain types of resets (e.g. The watchdog can only be configured and enabled once.The watchdog can be enabled and disabled multiple times and must be configured on each boot.When does the watchdog configuration get reset? Let’s walk through a quick list of things to check. Nuances in implementations can lead to unexpected issues later on. an ARM Cortex-M MCU) the behavior of the watchdog peripheral will be different. The peripheral is vendor specific so even if you are using the same chip family (e.g. When first configuring a hardware watchdog, it’s important to read the fine print in the datasheet about how the peripheral works. Identify system hangs and collect enough information to be able to root cause the underlying issue and deliver a fix. The embedded system should have a watchdog subsystem in place. Whether you are still in the development phase of a project or have millions of devices in the field, a UI task) is using so many CPU cycles that lower priority tasks (like a WiFi task) never get to run preventing sensor data from being published to your cloud service. One or more tasks become deadlocked because mutexes were grabbed in the wrong order or weren’t released.A hardware component (such as a HRM, Accelerometer, or NOR Flash Chip) is wedged and not.Memory gets corrupted and code winds up in an infinite loop.Some of the most common I’ve run into over the There are numerous ways an embedded device can hang. Usually “fed” by toggling a GPIO line from the MCU being monitored. NOTE: It also worth mentioning that for some systems where catching system hangs is missionĬritical, there are even dedicated ICs which can be used 2. The rationale here is if software is unable to reset the watchdog counter, the system is not running as expected and needs to be reset to get back to a sane state. This operation is usually referred to as “feeding”, “kicking”, or “patting” the dog.

Once enabled, the system software needs to reset the counter periodically to prevent the device from rebooting. The peripheral is typically disabled by default and it’s the programmers responsibility to configure and enable it in software. When the count reaches zero, the hardware will automatically reset the device. This peripheral is comprised of a counter which decrements automatically by the hardware each clock cycle. Most chip vendors include an isolated RTL block known as a “Watchdog Timer” in a MCU. Using GDB Python to prevent Software Watchdog Misfires.Configuring the NRF52 Hardware Watchdog.Examining the NRF52840 Hardware Watchdog Behavior.Enabling a Hardware Watchdog in a System.How do I find out if a watchdog reset took place?.What happens when the watchdog expires?.How does the watchdog behave with a debugger?.When does the watchdog configuration get reset?.

0 kommentar(er)

0 kommentar(er)